專家觀點:封閉 vs. 開放兩大系統

矽光子 CPO 產業正逐漸分化為兩大技術陣營。之光半導體技術長陳昇祐博士指出,矽光子元件單價高、容錯率低,若在封裝後才發現缺陷,報廢成本極高,因此測試環節大幅前移,「每顆必測」成為業界共識,推升探針卡、高階電測設備需求,也帶動材料與載板投資。

鴻海研究院半導體研究所洪瑜亨博士分析,AI 訓練與推理帶動頻寬需求急遽攀升,如今資料中心超過七成時間耗在資料搬運等待;當單通道速率突破 200G 後,銅線在損耗、功耗與模組體積上全面受限,迫使光學功能必須貼近運算晶片。由此市場分化出 LPO(線性驅動可插拔光學) 與 CPO 兩大路線,其中 CPO 將光引擎與 ASIC 直接整合至先進封裝,縮短訊號路徑、降低能耗,成為新世代 AI 資料中心的關鍵。

洪瑜亨補充,交換器大約每兩年帶寬就會倍增,但單通道速率需三至四年才翻倍,形成技術落差並推動 CPO 與 光學 I/O 加速發展。雖然 CPO 解決了傳統 QSFP+ 模組在體積與訊號失真上的限制,但高度整合也帶來 板翹曲與熱管理 挑戰,未來將朝更積體化的 光學 I/O 演進。

目前兩大生態系如下:

封閉系統:以 NVIDIA 為代表,強調垂直整合與專屬設計,並依靠台積電先進技術推進;與其合作的台廠包括上銓,掌握光纖陣列單元(FAU)與封裝能力。

開放系統:由 Broadcom 主導,採標準化與模組化,利於廣泛供應鏈參與,例如鴻海旗下訊芯-KY便與 Broadcom 合作,服務多家美系客戶。

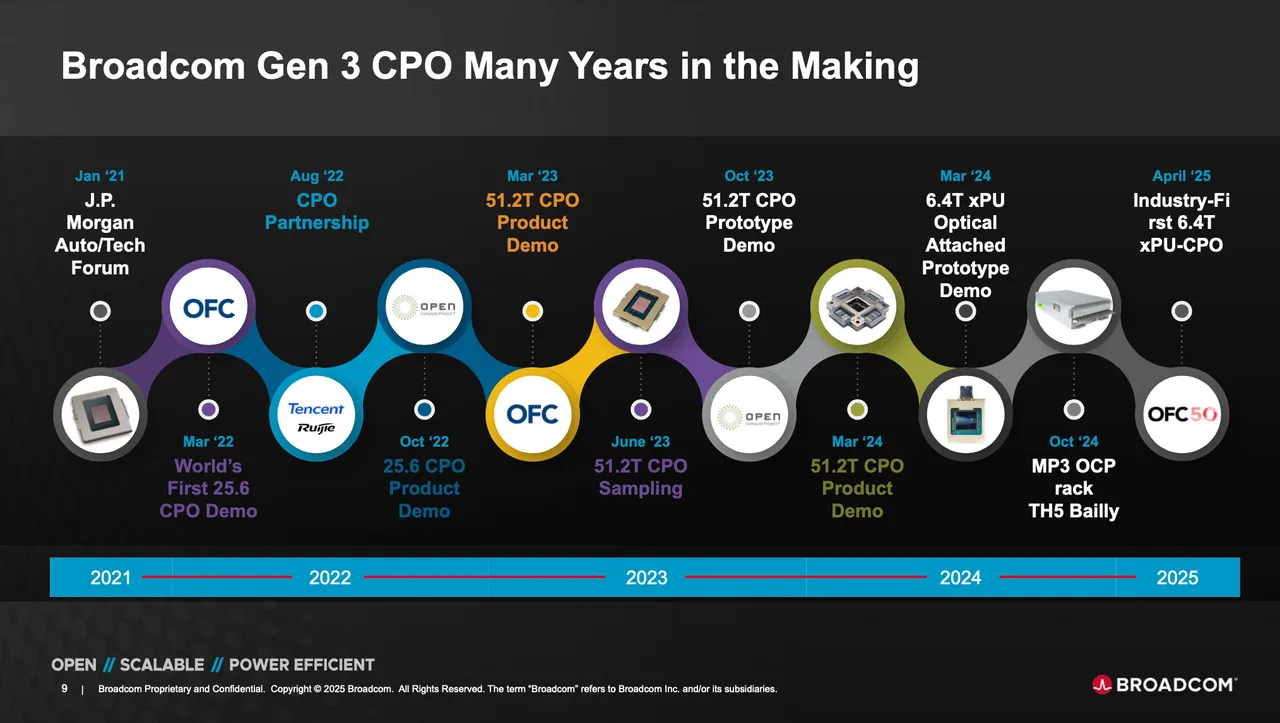

Broadcom領跑 CPO:開放生態加速商用

Broadcom 在光通訊與網路晶片耕耘已久,從 SerDes、高速交換晶片到光電整合技術,一直是超大規模資料中心的核心供應商。 Broadcom 光學系統副總裁 Manish Mehta 表示,AI 訓練與推論對網路需求呈指數成長,傳統銅纜難以支撐 Tbps 級資料吞吐,必須引入光學互連解決 I/O 與能效瓶頸。

Broadcom 自 2021 年布局 CPO,完成多代平台演進,2023 年起進入商用並推進 200G/Lane、400G/Lane 技術。CPO 將矽光子引擎與交換晶片同封裝,功耗可降 3.5~4 倍、整合密度提升百倍,讓過去需半機櫃的光模組縮小到「手掌大小」。 Manish Mehta 預估 2027 年將是 CPO 商用臨界點,屆時可望逐步取代傳統的可插拔式光收發模組(Pluggable Transceiver)成為主流。

Broadcom 同時積極推動 開放生態,選擇標準化介面與模組化設計,吸引雲端服務供應商、系統整合商與上游台廠參與,與 NVIDIA 專屬的封閉系統形成鮮明對比。

相關新聞:矽光子突圍01|光進銅退成趨勢 台灣AI十大建設+產業聯盟雙引擎發動

相關新聞:矽光子突圍02|加速落地!OBO到CPO三階段演進 2027商用爆發、台廠迎轉型契機

相關新聞:矽光子突圍03|AI資料中心升級兩大挑戰 台灣供應鏈助攻成「夢想實現之地」

NVIDIA:封閉式 GPU 平台推進光電封裝

相較 Broadcom 的開放策略,NVIDIA 正以自家 GPU 打造封閉式高速傳輸生態系。高級副總裁 Gilad Shainer 表示,AI 訓練與推論需要同時連接數十萬顆 GPU,任何延遲都可能讓運算停滯並推高成本,因此長期投入 InfiniBand 與 Spectrum-X Ethernet,持續推進更高頻寬與更低延遲的資料中心互連。

目前 NVIDIA 高頻寬連接仍以銅纜為主,但隨介面速度邁向 1.6T、3.2T,銅材受限於能耗與距離,轉向光學互連勢在必行。市場預期未來高階 GPU 平台,也就是明年將推出的 Rubin平台,將採用混合式光電封裝以突破光學 I/O (OIO)瓶頸。

在元件設計上,NVIDIA 偏好 MRM(微環調變器),利於 SoC 微縮與高整合,但需克服溫度敏感與熱補償挑戰,而NVIDIA則是依靠台積電一流的製造技術,讓 MRM 從一個風險較高的選項,成為可以進行的戰略賭注;Broadcom 則採MZI(馬赫增德干涉器),並以此為基礎打造的 MZM(馬赫增德調變器),雖體積較大但穩定性高。除了Broadcom,包括Marvell、Intel也都採用MZM解決方案。專家認為兩者無絕對優劣,矽光子仍處於多路線並行探索期。

台積電矽光子解方:COUPE結合CoWoS

台積電在 OCP APAC 與 矽光子國際論壇 上強調,為滿足 AI 客戶對高頻寬、低功耗需求,2026 年將導入 CPO 量產。公司以 12 吋 SOI(絕緣層上覆矽)晶圓 為核心,結合異質整合與先進封裝,讓矽光子真正走向商用。

三大技術優勢包括:

精準製程:波導線寬變異可控在 2 奈米內,確保微環共振腔等高靈敏元件一致性。

異質整合封裝:透過緊湊型通用光子引擎(Compact Universal Photonic Engine,COUPE) 與 CoWoS,實現數百通道光 I/O,降低功耗與延遲。

晶圓級測試:支援 Wafer-Level 與 Chip-Level 測試,提早篩選良率晶粒,降低封裝後重測與報廢成本。

根據台積電 2024 年北美技術論壇,COUPE 採用 SoIC-X 晶片堆疊技術,將電子裸晶直接堆疊於光子裸晶上,相較傳統堆疊方式,能達到更低電阻與更高能源效率。台積電與 Ansys、Synopsys、Cadence 等 EDA 廠商合作推進,2025 年將完成支援小型插拔式連接器的驗證,2026 年整合 CoWoS 成為 CPO 元件,讓光連結直接導入封裝。

台積電指出,CPO 商業化仍面臨三大挑戰:製程良率控制、測試標準缺乏及封裝熱管理。但憑藉高良率製程、成熟測試平台與異質整合封裝能力,台積電已成 Broadcom、NVIDIA 等系統大廠不可或缺的核心夥伴,被視為推動矽光子量產的關鍵推手。

投資觀察:2027商用關鍵點 台灣供應鏈迎新紅利

CPO 與矽光子已從實驗室走向商用化前夜,Broadcom 推動開放生態、NVIDIA 鞏固封閉系統,兩大路線加速分化;台積電憑藉製程、封裝與測試整合穩居全球核心供應商。法人普遍認為 2027~2028 年是商業化關鍵點,屆時無論是測試與封裝、材料與 SOI 晶圓,還是模組與光學元件,台灣廠商都將在全球 AI 高速互連浪潮中扮演不可或缺的角色,成為下一波 AI 投資布局的受益族群。

點擊閱讀下一則新聞

點擊閱讀下一則新聞