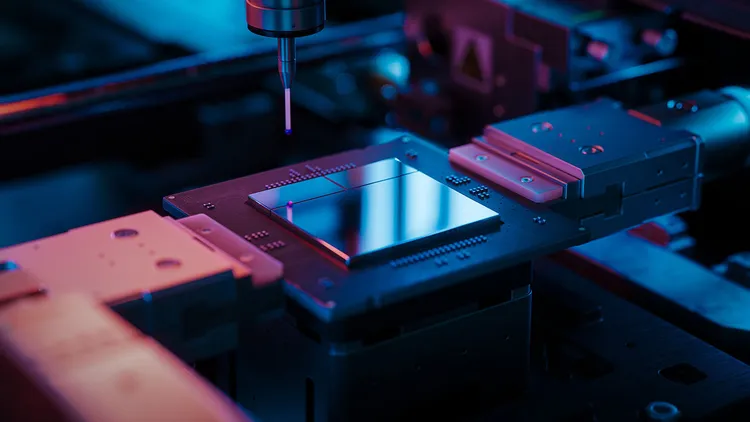

西門子指出,半導體設計正從 2D 持續邁向 2.5D、3D 堆疊架構,電晶體密度與設計規模急遽擴張,使測試向量激增,ATE(自動化測試設備)成本與測試時間同步攀升。加上測試引腳資源受限,若無法強化現有測試基礎架構,將難以跟上 3D IC 與 chiplet 快速崛起所帶來的測試需求。

Tessent IJTAG Pro 正是為此而生。透過平行化資料通道,取代傳統串列方式,其高頻寬設計可支援更大規模的測試資料傳輸,有助提升邏輯測試效率,並改善混合訊號 IP 與內建自我測試(BIST)的測試效能。

西門子數位設計創作平台資深副總裁暨總經理 Ankur Gupta 表示,此次升級直接對準客戶的最大痛點,也就是測試時間,Tessent IJTAG Pro 以 SSN 加速測試資料流動,不僅能降低測試成本,也提供符合下一代半導體演進需求的彈性,無論是單晶片或完整 3D 封裝,都能獲得顯著效益。

Google 資深工程經理 Srinivas Vooka 強調,高頻寬 IJTAG 的傳輸速度遠超串列架構,使測試套用時間明顯縮短,對複雜 IP 測試尤具關鍵價值。

西門子補充,新方案若搭配 Tessent AnalogTest 軟體,可進一步提升整體測試頻寬與功能完整性,展現其在 3D IC 時代加速量產準備的企圖。

點擊閱讀下一則新聞

點擊閱讀下一則新聞

三星曾來台勸退!台灣半導體「造山者」回顧DRAM產業自主關鍵戰役