經濟部產業技術司副司長周崇斌指出,生成式AI與高速運算推升資料中心流量自2010年至2024年暴增逾70倍,進而驅動高速傳輸與高效能晶片需求。技術司近5年投入近400億元,聚焦AI、高效能運算(HPC)、矽光子、先進封裝與化合物半導體,推動晶片軟硬整合與自主製造,強化供應鏈韌性。

工研院已開發國內首款1.6 Tbps矽光子光引擎模組,並與日月光合作建構「矽光半導體開放式平台」,提供設計到封測的一站式服務。同時,全球首創的3D客製化晶片模組則讓晶片如積木般快速組合,縮短七成開發時間並降低成本,已服務逾133家業者,帶動21億元投資。

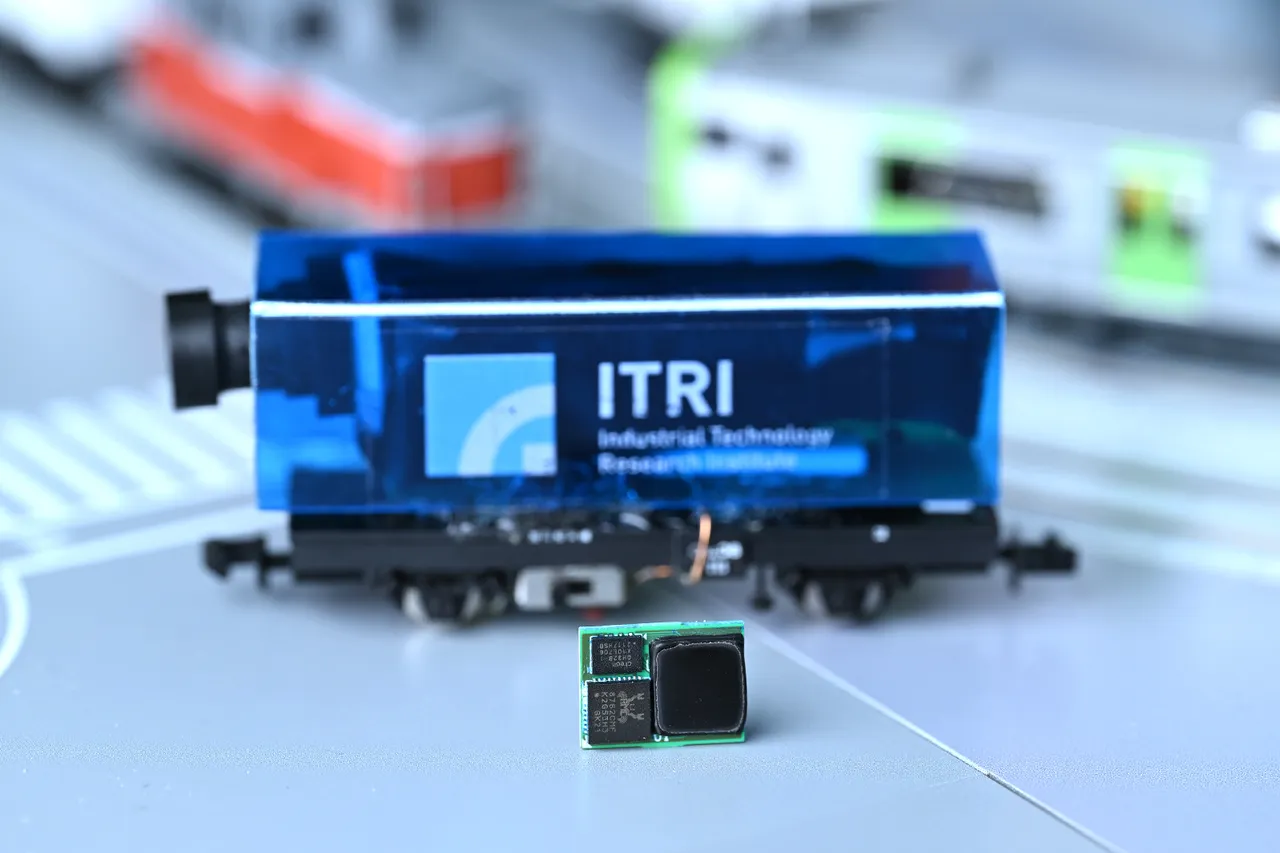

工研院副總暨電光系統所所長張世杰表示,傳統光電架構逐漸逼近極限,工研院突破性開發矽光子光引擎模組,整合光電元件以提升頻寬與效率,並鏈結產業打造開放平台,協助業者進軍國際市場。另一項全球首創的3D客製化晶片模組,將半年以上的開發縮短至12週,體積縮小三成仍能整合多種運算與傳輸功能,並已技轉巽晨國際,攜手欣興電、鼎晨科技建置試產線,成為AIoT產業的重要推力。

矽光子技術國際接軌 加速高速傳輸新里程碑

工研院成功研發臺灣首款 1.6 Tbps 矽光子光引擎模組,效能已達國際水準,能對標 NVIDIA GTC 2025 展示的最新進展。其核心優勢在於藉由矽光子結合先進封裝技術,將光電元件高度整合,使資料可即時傳輸,大幅降低延遲、提升頻寬與效率,為資料中心與高效能運算所需的超高速、低功耗傳輸能力奠定基礎。工研院並與日月光及國內業者串聯,打造「矽光半導體開放式平台」,結合 2.5D/3D 高密度設計與 224Gbps/Lane 多通道量測能力,並以異質封裝提供完整解決方案。透過一站式服務,臺灣業者能更快切入全球高速傳輸市場,搶佔下一代資料中心與 AI 運算的戰略藍海,強化在全球半導體供應鏈的競爭地位。

全球首創3D客製化晶片通用模組 小晶片推動AIoT加速上市

傳統系統級封裝(SiP)開發時程往往需半年至一年,且因反覆驗證而影響上市進度。工研院全球首創「3D 客製化晶片通用模組」,透過預製連線基板與內嵌主動式切換晶片,能將開發時間縮短至 12 週,效率提升七成。此技術不僅制定公規基板並符合 JEDEC 國際標準,確保高良率與低複雜度,還能如積木般靈活組合,讓業者無需從零設計,即可快速推出新品。模組體積縮小三成,仍能整合 Full-HD 影像處理、AI 運算及 RF 傳輸等功能,適用多元感測器與 AIoT 應用。目前已成功技轉巽晨國際,並攜手欣興電、鼎晨科技建置試產線,預計覆蓋七成 AIoT 市場應用,並帶動超過 21 億元投資,成為臺灣 AIoT 產業的加速引擎。

顯微干涉同步檢測模組 一站掌握晶圓尺寸與形貌

隨著先進封裝疊層製程日益複雜,傳統檢測方式需多台設備才能分別掌握尺寸(2D)與形貌(3D)資訊,導致時間與成本增加。工研院研發的「顯微干涉同步檢測模組」創新整合 2D 顯微與 3D 干涉於單一光路設備中,能省去多站搬運與重新對位程序,檢測時間縮短 50%,設備成本降低 40%。該模組具備 400μm 大範圍與小於 0.5nm 的奈米級高解析分析能力,能精準應對先進封裝日益嚴苛的檢測需求。技術已協助承湘科技開發 5G 天線模組檢測設備,並與台灣暹勁合作開發 HAMR 硬碟檢測設備,展現跨領域應用價值。此模組的導入不僅提升產線良率,更為臺灣檢測設備技術樹立新標竿。

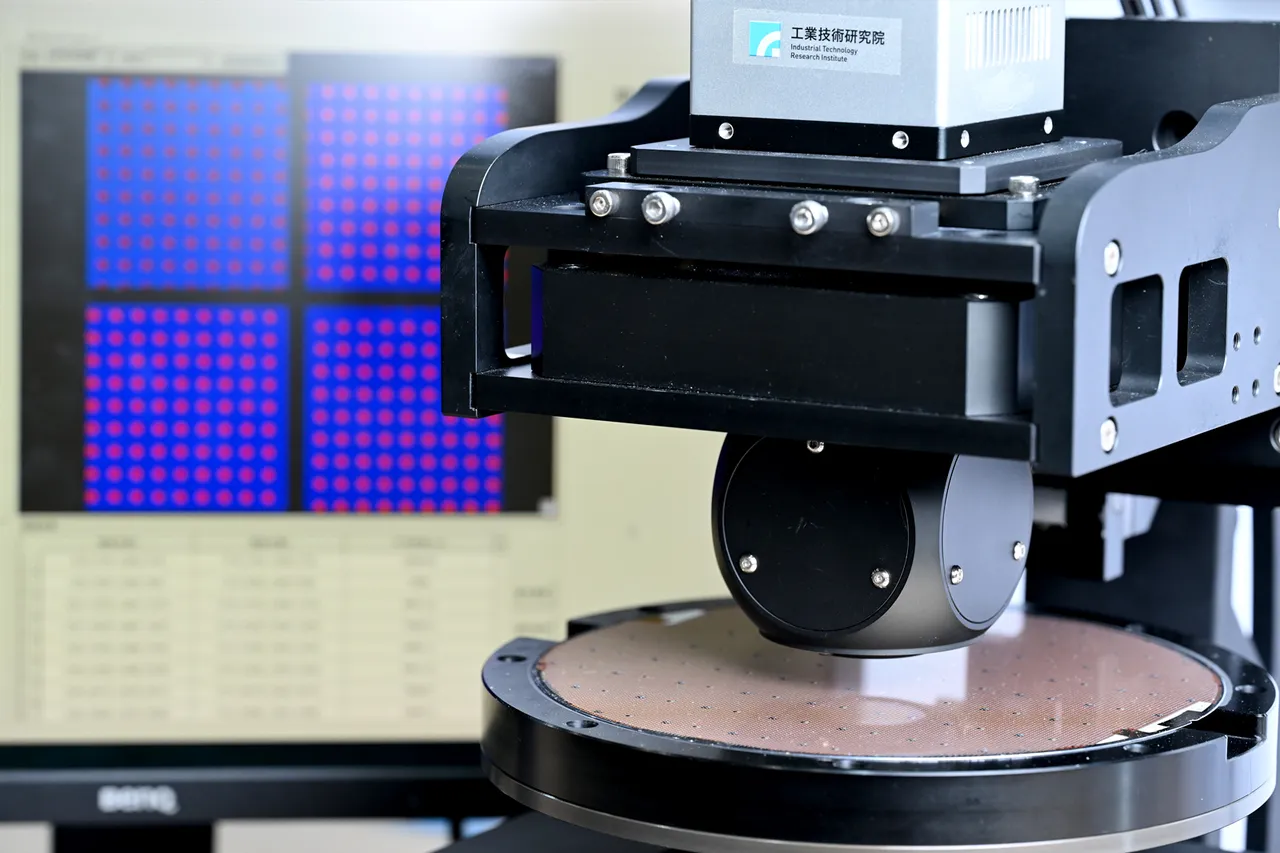

陣列視野×奈米精度:次世代封裝高效檢測方案

全球半導體與電子製程先進封裝產能持續擴張,對檢測效率的需求日益提高。工研院首創微型化陣列式鏡組技術,開發 2×2 多鏡頭自動化顯微校準方案,實現奈米級檢測的高效突破。相較傳統單鏡頭檢測系統,本技術擴大四倍檢測視野,仍能維持高精度,並將檢測效率提升 4 至 10 倍,適用於 μLED、被動元件及先進封裝產業的線上檢測。該技術已與國內設備商與系統整合商合作,完成雛型設備開發,並通過國家標準技術研究所(NIST)標準件、μBump 與 μLED 樣品驗證。此創新方案能有效解決產線大規模檢測的瓶頸,協助臺灣在高階檢測市場搶得技術先機。

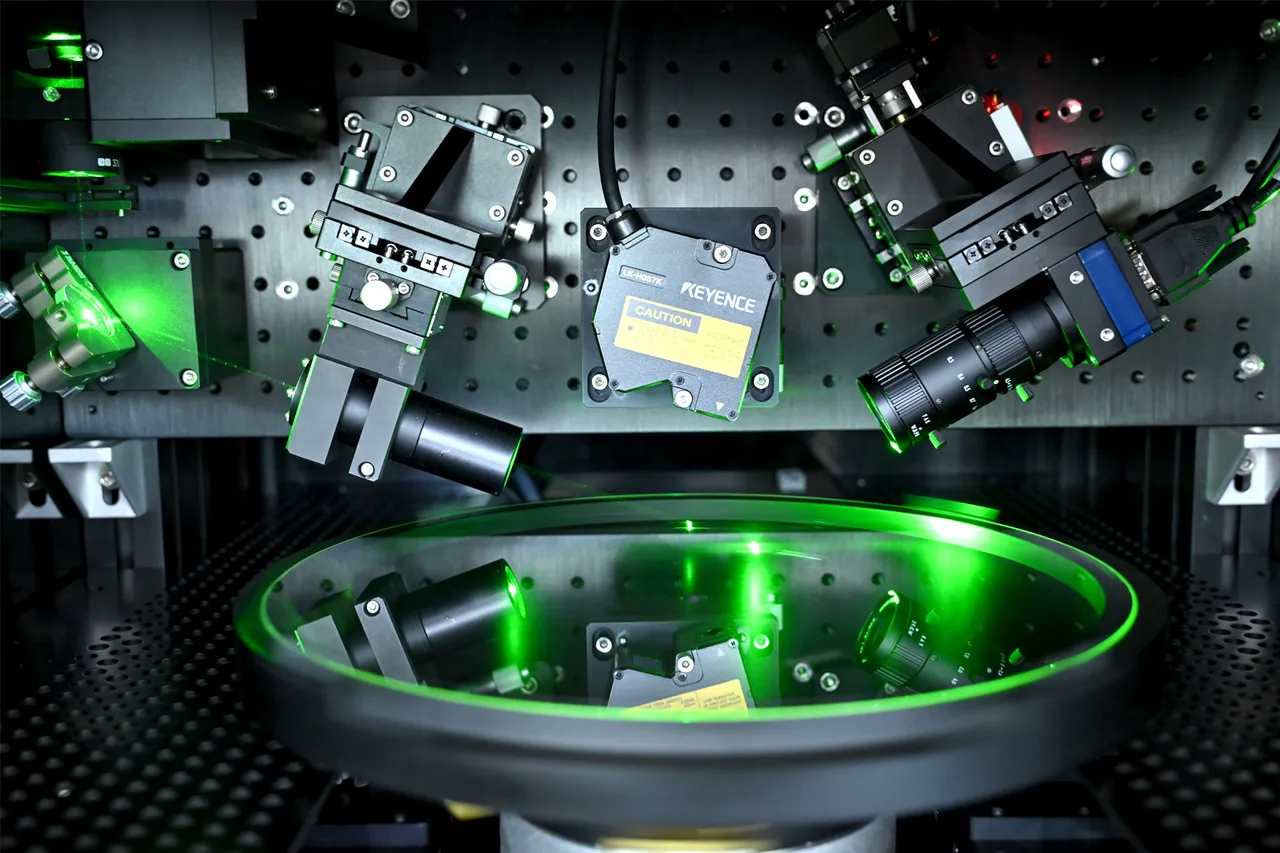

圓表面粒子檢測設備 精準監控透明晶圓品質

晶圓表面粒子檢測是半導體製程中的關鍵一環,但現有光學檢測技術普遍速度慢、靈敏度不足,難以滿足透明晶圓與更小粒徑需求。工研院自主開發「傾斜入射雷射散射光學模組」及專屬演算法,可應用於矽、碳化矽與玻璃材料,檢測粒徑最小可達 0.2 μm,並能在 4 分鐘內完成 8 吋晶圓檢測。該技術目前已協助國內晶圓廠導入,透過晟格科技與和亞智慧科技,應用於玻璃載板與 SiC 晶圓線上檢測,協助產業提升良率與降低成本。同時,這項成果也彌補了國際上缺乏透明晶圓檢測標準的空缺,讓臺灣不僅能自主掌握檢測設備開發,還能進一步強化供應鏈韌性,提升在先進半導體製程的國際話語權。

點擊閱讀下一則新聞

點擊閱讀下一則新聞